반도체 공정

1) 반도체 공정의 흐름

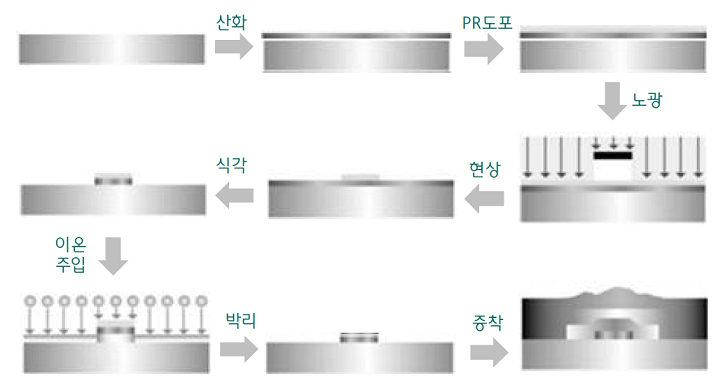

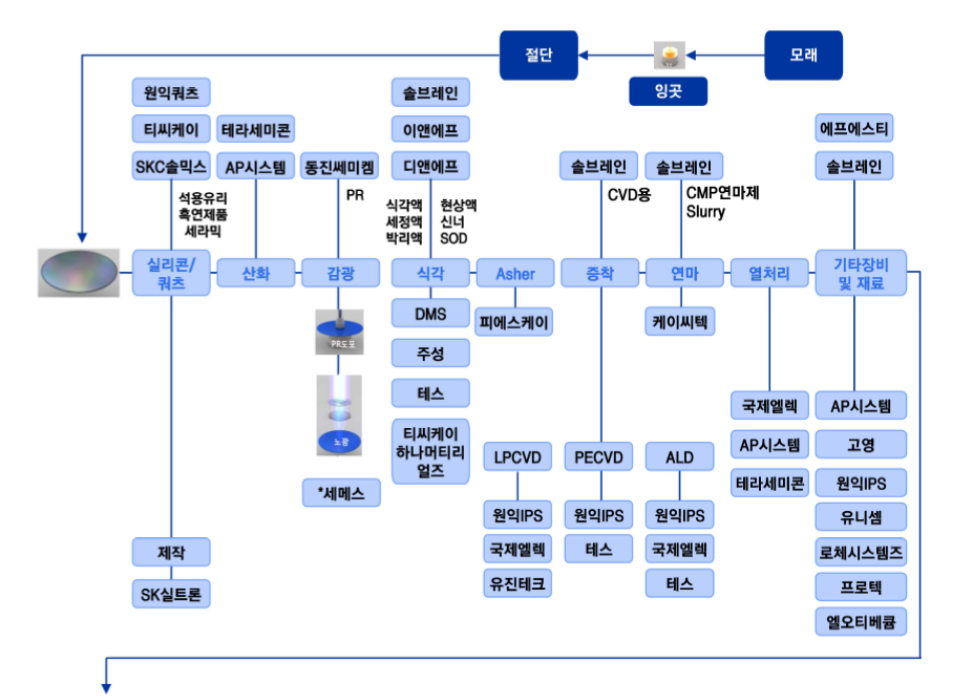

반도체 공정(fabrication)은 웨이퍼에 패턴을 형성하기 위한 산화, 노광, 식각, 이온주입,

박리/세정, 증착, 연마, Gate 형성의 전공정과, 이후에 칩별로 잘라서 패키징하고

테스트하는 후공정으로 구분된다.

그림 . 반도체 전공정과 후공정

전공정은 보통 산화, 노광, 식각, 이온주입, 박리/세정, 증착, 연마의 순서로 이야기 한다.

하지만 반도체는 각 공정을 1회씩 걸쳐서 완료되는 것이 아니라 앞서 언급한 공정들이

선택적으로 반복되서 진행된다.

예를 들어, 소자를 구성하는 공정에는 식각 공정 후 이온주입을 통해 전기적 특성을 띄는 소자를

형성하지만,금속을 통해 전기적인 배선을 형성하는 경우는 이온주입공정을 거칠 필요가

없으므로, 식각 후 다시 증착 공정을 거치게 된다.

그림 . 목적에 따른 공정 순서의 차이

2) 웨이퍼의 제조

그림 . 웨이퍼의 제조

반도체는 조건에 따라 전기전도도를 변화시킬수 있는 규소(Si), 게르마늄(Ge)등의

물질을 이용한다.

현재는 경제적인 이유에서 모래에서 추출 가능한 규소(Si)만을 사용하고 있다.

규소를 반도체 제조를 위한 원판형태로 형성한 것이 실리콘 웨이퍼이다.

웨이퍼 제작은 실리콘을 녹여 액체상태로 만들고, 이를 실리콘 기둥(ingot)으로 성장시켜

절단하는 방식으로 제조한다.

기둥을 성장시키는 과정에서 실리콘의 정제도 동시에 진행된다.

실리콘 기둥을 성장시키는 방법에는 초크랄스키법(Czochralski, CZ)과

플로팅 존법(Floating Zone, FZ)을 주로 사용한다.

초크랄스키법은 도가니를 이용해 실리콘을 용해한뒤, 용액안에 실리콘 막대를 회전시켜

서서히 끌어올려 가는 방법이다.

큰 크기의 웨이퍼를 만드는데 용이하나 도가니안의 산소 혼입으로 오염이 쉽다는 단점이 있다.

플로팅 존법은 실리콘 주위를 부분적으로 용해하며 웨이퍼를 제조하는 방법으로 높은 전도성과

고순도의 결정을 만들수 있으나 고비용이라는 단점이 있다.

성장시킨 실리콘 기둥을 균일한 두께로 절단하여 웨이퍼를 제작한다.

절단 직후 웨이퍼의 표면은 흠결이 있고 거칠기 때문에, 이를 열처리하고 연마하는

작업이 필요하다.

그림. 실리콘 웨이퍼 제조과정

3) 산화(성막)

그림. 산화막 생성

산화는 전기로 안에서 실리콘 웨이퍼에 산소와 수증기를 투입하여, 실리콘 표면에 산화막

(SiO2)를 형성하는 공정이다.

막을 형성하기 때문에 성막공정이라고도 한다.

산화막은 반도체에서 1) 불순물이 선택적으로 주입될 수 있도록 하거나, 2) 반도체의 절연물질,

3) 커패시터의 유전물질 및 층간 절연물질, 4) MOSFET 구조의 Gate 산화막,

5) 외부 환경으로부터의 기판을 보호하는 역할을 담당한다.

산화과정은 습식산화와 건식산화로 구분한다.

건식산화는 건조한 산소를 사용해 산화막을 형성하는 방법이다. 사용되는 물질로 산소(O2)와

이를 운반하는 캐리어 역할을 수행하는 질소(N2), 실리콘에 존재할 수 있는 오염원인

나트륨(Na) 이온을 제거하기 위한 염산(HCl)이 사용된다.

건식 산화는 막질이 우수하고 산화막의 두께 제어가 용이하다. 다만, 습식 산화에 비해서

느린 속도가 단점이다.

건식 산화막은 MOSFET(Metal Oxide Semiconductor Field Effect Transistor,

전계효과트랜지스터)에 Gate 산화막 형성시 주로 사용된다.

습식산화는 고온의 전기로에서 수소와 산소의 불꽃반응을 이용하여 수증기를 공급하는 방식이다.

산화막의 성장속도가 빠르나 그만큼 산화막질이 우수하지 못하고 두께 제어가 쉽지 않다.

사용되는 물질로는 염산(HCl), 질소(N2), 산소O2) 외에 수소(H2)가 있다.

주로 웨이퍼필드(표면)의 산화시 사용하는 방식이다.

그림. 건식 산화 장비 구조

그림. 습식 산화 장비 구조

4) 포토 공정

그림. PR도포, 노광, 현상

포토 공정은 웨이퍼 위에 반도체 회로를 그려 넣는 공정이다. 포토 공정은 필름을

인화지에 인화하는 방법과 동일하다.

웨이퍼 위에 빛에 반응하는 감광제(Photo Resist)를 도포한 뒤, 노광기를 이용해

마스크(회로가 그려진 기판)를 통해 빛을 전사한다.

그 후 감광제에 열을 가하여(Bake 과정) 현상하고, 식각 공정을 거친 뒤 남은 포토레지스트를

제거(박리)해 회로를 웨이퍼 위에 설계하는 것이다. 포토 공정은 수나노의 회로를 빛을 이용해

웨이퍼 위에 전사 하기 때문에 공정시 청정도에 따라 칩의 수율에 큰 영향을 미친다.

감광제는 빛 에너지에 의해 분해되는 화학 물질을 용매에 용해시킨 혼합물이다.

감광제는 현상시 노광되는 부분이 제거되는 양성감광제와 노광되지 않은 부분이 제거되는

음성감광제로 구분된다.

음성감광액은 낮은 해상도로 인해 반도체 공정에는 잘 사용되지 않으나, 소자의 크기가

큰 디스플레이 공정에서 주로 활용된다.

마스크는 쿼츠(석영)기판에 크롬(Cr)으로 설계한 패턴으로 구성된다.

크롬층이 있는 부분은 빛을 통과시키지 않아 설계한 패턴을 웨이퍼에 전사하는 반도체 부품이다.

빛을 비추는 노광기(Stepper)는 광원에 따라 구분되는데, 광원에 따라 구현할수 있는

최소 선폭이 결정된다.

나노미터급인 빛의 단파장 길이는 G선, I선, 불화크립톤(KrF), 불화아르곤(ArF), F2 레이저,

Ar2 레이저, 극자외선(EUV) 순으로 짧은 파장을 가지고 있다. 미세공정 전환이 진행될수록

파장이 짧은 광원을 사용해야 한다.

10나노공정 이하에선 노광과정을 여러번 반복하여 패턴을 형성하는 멀티패터닝

방식이 사용되고 있다.

그림. 포토 공정 구조

그림. 광원에 따른 파장

5) 식각 공정

그림. 식각

식각 공정은 포토 공정을 통해 형성된 패턴에 따라, 필요한 부분을 얇게 만들거나

제거하는 과정이다.

식각 공정을 거쳐야만 비로소 사진 공정에서 그려진 회로가 웨이퍼에 새겨진다.

사진공정과 관계없이 불필요한 박막을 제거하는 것 또한 식각 공정에 포함된다.

식각 공정은 화학약품을 사용하는 습식식각과 가스를 사용하는 건식식각으로 구분된다.

습식식각은 제거하고자 하는 물질을 식각할 수 있는 화학용액(식각액, etchant)을

수조(Wet bath)안에서 웨이퍼와 반응시키는 방식이다.

용액안에서 식각이 진행되므로, 수평과 수직방향으로 모두 식각이 이루어지는

등방성 식각이 진행된다.

이러한 성질 때문에, 포토 공정으로 형성한 패턴보다 크게 식각이 되는 현상이 발생하여,

공정전환으로 최소선폭이 미세화될수록 적용하기 어렵다.

그러나 습식 식각은 목표로 하는 특정 물질만 식각하는 선택성에서 탁월하다.

우수한 선택성 때문에 습식식각은 패턴 형성과 무관하게 불필요한 박막을 제거하는데 용이하다.

건식 식각은 식각하고자 하는 대상 물질과 반응하는 가스를 이용하여 식각하는 방식이다.

가스의 반응을 일으키기 위해 전기적인 에너지를 가하여 플라즈마 상태로 전환한 후,

이때 생성되는 이온을 이용해서 식각 반응을 일으킨다. 이온의 직진성 때문에, 수직으로만

식각이 진행되는 이방성 식각이 이루어진다.

이에 따라 사진공정에서 형성된 패턴의 크기와 동일하게 식각이 이루어져, 미세한 소자를

제조하는 반도체 식각 공정에서 다루기 용이하다.

다만, 이온의 물리적인 운동을 통해 식각이 진행되어 대상 물질외에도 식각이

이루어져 습식 식각에 비해 선택성은 떨어진다.

표. 박막 종류에 따른 주요 식각액/식각용 가스

그림. 식각 공정 모식도

그림. 식각의 등방성, 이방성

- 국내 유일 반도체 건식 식각장비 업체 : 에이피티씨 (089970)

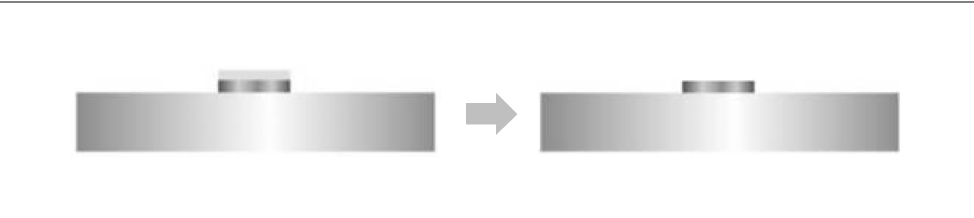

6) 박리/세정

그림. 박리/세정

박리 공정은 식각공정 후 남은 감광액(Photo Resist)를 제거하는 작업이다.

Strip 공정이라고도 불린다.

식각과 동일하게, 박리 장비 또한 습식 박리와 건식 박리로 구분된다.

습식박리는 감광액을 분해하는 박리액을 사용하여 화학적 반응을 통해 제거하는 방식이다.

습식박리의 박리액은 주로 H2SO4(황산), H2O2(과산화수소) 등을 사용한다.

건식식각이 이루어 진 경우, 감광액이 플라즈마 가스 및 이온과의 접촉, 충돌로 변질되어 쉽게

제거되지 않는 경우가 발생한다. 이런 경우엔 산소 플라즈마를 사용하는 건식박리를 이용한다.

산소를 사용한 공정이기 때문에 웨이퍼 및 금속의 산화가 일어날 우려가 있다.

습식박리와 건식박리를 병행하여 처리하기도 한다.

세정은 반도체 웨이퍼 위의 먼지, 사람의 침, 표피, 공정 후 남은 화학 물질등의 오염원을

제거하는 공정이다.

한 단계 공정이 끝날 때마다 세정작업을 거치게 된다.

현재 반도체 세정기술은 70년대 RCA사에 의해 개발된 기술을 기본으로 하고 있다.

RCA 세정 방법은 H2O2(과산화수소)를 기본으로, NH4OH를 같이 사용하는

SC1(Standard Cleaning 1)과 HCl를 사용하는 하는 SC2(Standard Cleaning

2)의 두단계로 이루어진 습식 세정 방법이다.

습식 세정 방법은 필연적으로 세정 후 다음 공정으로 이동시 오염물질에 다시 노출 될

가능성을 가지고 있다.

이를 해결하기 위해 HF, O3, Cl2. AR등의 플라즈마 가스를 사용하는 건식 세정 방식을

사용하기도 한다

건식 세정 방식은 진공상태에서 이루어져, 대부분의 공정과 같은 시스템 내에서 진행이 가능하다.

그림. 오염원에 따른 공정에서의 문제 발생

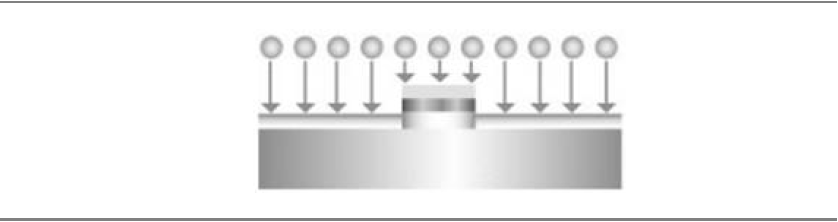

7) 확산(이온주입)

그림. 이온주입

반도체의 주원료인 실리콘(Si)의 전기적 특성을 인위적으로 변화시키기 위해선 Si이 아닌 다른

불순물(Dopant)을 주입하여야 한다. 주로 주기율표상 3족 원소와 5족 원소를 사용한다.

3족원소를 주입할 경우 실리콘과 결합한 뒤 하나의 전자가 남게되고, 이러한 잉여전자의

흐름으로 전도성을 띄는 N(Negative)형 반도체가 만들어 진다.

3족 원소를 실리콘에 결합하면 실리콘과 결합시 하나의 전자가 부족하여, 부족한 공간을

채우려는 전자의 흐름으로 전도성을 띄는 P(Positive)형 반도체가 만들어 진다.

보편적으로 P형 반도체를 생성시엔 붕소(B),N형 반도체를 생성시엔 인(P)을 불순물로 사용한다.

불순물을 웨이퍼에 주입하는 방법은 주로 확산법과 이온주입법을 사용한다.

확산법은 입자가 농도가 높은쪽에서 낮은쪽으로 퍼져나가는 현상을 이용한 방법이다.

고온의 챔버 내에서 불순물과 웨이퍼를 가열하면, 웨이퍼의 표면에서부터 내부로

불순물이 침투한다.

불순물의 종류는 가스, 액체, 고체 상태 모두 사용될 수 있으며, 불순물을 운반하기위해 N2(질소),

Ar(아르곤)과 같이 화학반응을 일으키지 않은 비활성기체와 혼합되어 사용된다.

확산법을 이용한 불순물은 웨이퍼 내에 균일하게 주입되는 특성을 가지고 있다.

이온 주입(ion implantation)은 불순물을 이온화시켜 고전압을 이동하여 이온을 가속,

이온빔의 형태로 웨이퍼에 주입하는 방법이다.

이온을 가속시키는 전압을 조절하여 속도를 결정할 수 있으며, 이에 따라 불순물이 웨이퍼에

주입되는 깊이를 조정할 수 있다.

또한 웨이퍼의 영역별로 서로 다른 불순물을 주입할 수 있어 MOSFET등의 제조공정에서

소스 및 드레인 형성, Well 형성 등에 용이하다.

다만 이온을 주입하는 과정에서 웨이퍼 표면에 의도치 않은 손상을 발생시키기

때문에,가열을 통해 손상을 정비하는 어닐링(Anneling) 공정이 필요하다.

특히, 불필요한 불순물의 확산을 막기 위해 웨이퍼 표면만 빠르게 가열하는 방식을

RTP(Rapid Thermal Process) 혹은 RTA(Rapid Thermal Anneling)라고 한다.

그림. 확산공정 모식도 그림. 이온주입후 Anneling 처리

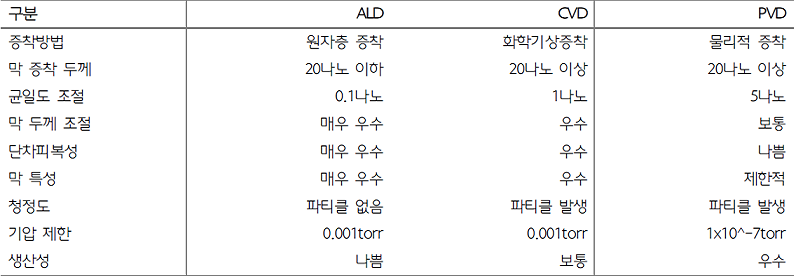

증착이란 반도체 웨이퍼위에 원하는 물질을 얇은 막(박막, Thin film)형태로 형성하는 공정이다.

크게 화학적 반응이 관여하지 않고 재료를 물리적으로 기화시켜 증착하는 물리기상증착(PVD)과,

형성하고자 하는 박막 재료를 수성하는 원소로 된 가스를 공급해 표면에서의 화학반응을 통해

증착하는 화학기상증착(CVD)이 있다.

물리기상증착(PVD) 방식은 원하는 물질을 기화시키는 방법에 따라 열증발법, 전자빔 증발법과

플라즈마를 통해 높은 에너지의 입자를 증착 물질에 조사하는 스퍼터링(Sputtering)방법등이 있다.

기체상태의 물질이 웨이퍼에 도달해 증착하게 되므로, 박막의 순도를 위해 진공 상태에서

공정이 이루어져야 한다.

화학기상증착(CVD) 방식은 원료 가스의 양을 제어하여 막 두께 제어 및 증착돤 박막의 성분을

조절하는데 용이하다.

장비가 요구하는 압력에 따라 APCVD(Atmospheric Pressure CVD)와

LPCVD(Low Pressure CVD)가 있다.

압력이 낮을수록 가스의 수송속도가 높아져 균일한 막 두께를 얻을 수가 있지만, 진공에 가까운

상태를 유지하는데 비용이 발생한다.

APCVD, LPCVD는 화학반응을 일으키는 에너지원으로 열을 사용하는 열 증착법이며,

에너지원으로 열 대신 플라즈마를 이용하는 PECVD(Plasma Enhanced) 방식도 사용한다.

ALD는 화학반응 중 화학흡착에 의해서 막을 형성시키는 방식이다.

화학흡착에 의한 박막형성은 원자단위의 아주 얇은 막을 형성할 수 있어 복잡한 구조물에

대해서도 100% 형태를 유지하는 장점을 가지고 있다.

표. 증착 방식별 특성 8

그림. CVD Mechanism 그림. ALD Mechanism

화학기상증착(CVD) 방식에는 화학 반응에 필요한 가스 소재가 필요하다.

CVD 공정에 사용되는 가스는 증착하고자 하는 물질을 가지고 있는 전구체(Precursor)와,

반응 후 발생되는 부산물을 챔버내에서 제거하는 세정용 가스로 구분된다.

전구체(Precursor)는 반도체 박막의 성분을 포함하고 있는 화학 가스이다.

용도에 따라 Capacitor용 높은 정전용랑을 갖는는 High-K, 낮은 유전율을 층간 절연물질용

Low-K, 금속배선용 메탈전구체 등 형성하고자 하는 박막의 목적에 따라 수십가지

종류로 구분된다.

많이 사용되는 증착용 가스로는 금속배선을 위한 텅스텐 증착용 육불화텅스텐(WF6),

폴리실리콘 형성용 모노실란(SiH4),질산막 형성용 암모니아(NH3) 등이 있다.

세정용 가스는 CVD공정에서 화학반응이 일어난 후, 챔버 내에 남아있는 화학반응의 부산물을

제거하는 역할을 한다.

삼불화질소(NF3)가 대표적이며, 그외에 불소계 가스인 사불화탄소(CF4),

육플루오린화황(SF6) 등이 있다.

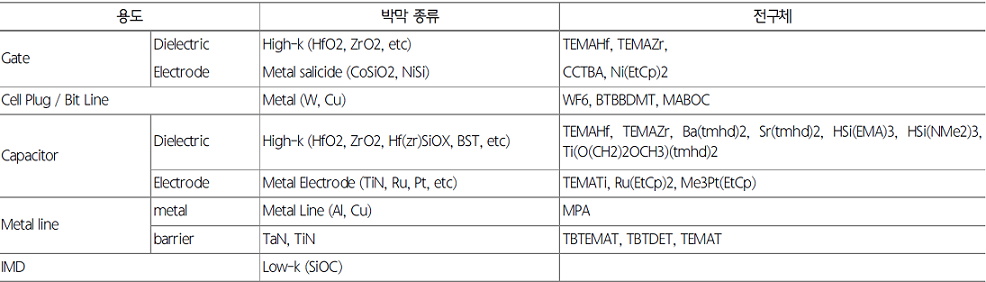

표. 박막 용도에 따른 대표 전구체

9) 연마/CMP(Chemical Mechanical Polishing)

그림. 연마/CMP

CMP 공정은 슬러리를 이용하여 산화 및 증착이후의 웨이퍼 표면을 화학적/물리적으로 갈아서

평탄화 시키는 과정이다. 슬러리는 미세 고체입자가 포함된 현탁액을 말한다.

슬러리가 웨이퍼 표면을 더 부드럽게 만들고 pad를 이용하여 기계적으로 표면을 갈아낸다.

CMP 슬러리는 연마하고자 하는 막질의 종류에 따라 나뉘며, 크게는 반도체 산화막(Oxide)용

슬러리와 메탈 슬러리로 구분할수 있다.

산화막용 CMP는 슬러리는 주로 실리카(SiO2), 세리아(CeO2)가 주요 사용된다.

전통적으로 유리 렌즈 가공에 많이 사용되던 세리아 슬러리는 실리카에 비해 입자 크기가 커

연마 속도가 3배이상 높아 양산성 측면에서 유리하다.

다만 웨이퍼 표면에 상처를 입히기 쉽개 때문에 과거에는 잘 사용되지 않았다.

미세공정전환에 따라 질화막에 대한 연마가 중요해지면서,질화막 선택비가 높은 세리아

슬러리가 주목받고 있다.

현재는 주로 STI(Shallow Trench Isolation, 회로 내에서 소자 사이를 구분하는 절연체)

형성에 주로 사용된다.

국내 케이씨텍이 세리아 슬러리를 주로 공급하고 있다.

메탈 슬러리는 희석된 산화제(Oxidizer, Fe(CN)6, H2O2)에 알루미나(Al2O3)

입자가 주로 사용된다.

주로 소자 Contact용 텅스텐(W)막 및 배선 형성 물질인 구리(Cu), 알루미늄(Al) 연마에 사용된다.

일반적으로 금속막은 산이나 알칼리에 취약한 박막 구조를 지니고 있어 메탈 슬러리에는

이를 막기위한 화학 물질이 포함되어 있어야 한다.

그림. CMP 장비 구조 그림. CMP 공정 Mechanism

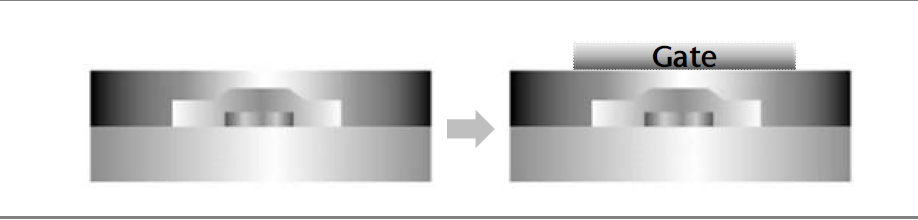

10) 게이트 형성

그림. 게이트 형성

반도체 제조과정은 웨이퍼 위에 산화, 포토, 식각, 박리, 세정, 증착, 연마등의 공정을 필요에 따라

반복하면서 회로를 그려나가는 과정이다.

회로에는 트랜지스터, 다이오드, 저항, 인덕터, 콘덴서등의 역할을 하는 소자들이 모두 그려진다.

수많은 소자를 칩 하나에 구현하여 직접 회로(IC)라고 부른다.

이러한 소자들 중 가장 핵심적인 역할을 하는 소자가 트렌지스터이다.

트렌지스터는 전류의 증폭과 스위치 역할을 수행하는 소자이다.

최근 반도체 소자에 주로 이용되는 트렌지스터는 MOSFET(전계효과 트렌지스터)이다.

MOSFET은 소스(Source), 드레인(Drain), 게이트(Gate)의 세부분으로 구성되어 있으며,

소스와 드레인 사이의 통로를 통해 전류의 이동이 이루어진다. 이 통로는 산화막을 통해

게이트와 연결되어 있다.

통로와 게이트 사이에 산화막이 있으므로 게이트와 통로간 전자의 이동은 불가능하다.

게이트에 전압을 걸면, 이 때문에 발생하는 자기장이 통로 안의 전자의 흐름을 제어하게 된다.

게이트에 작용하는 전압을 변경하여 통로에 흐르는 전류의 양을 조정하는 트렌지스터의

역할을 하게 된다.

통상적으로 소스, 드레인을 N형 반도체로 형성하면 통로는 P형 반도체로 형성한다.

N형, P형을 반대로 형성하여도 동일한 원리로 작동한다.

메모리용 반도체인 DRAM, NAND는 트렌지스터의 Gate부에 인위적인 전압이 아닌 전하를

축척하는 소자를 적용한 반도체이다.

DRAM은 Gate에 축전기(Capacitor)를, NAND는 Gate에

플로팅게이트(Floating Gate)를 설치한다.

축전기와 플로팅게이트는 전하를 축적하여 자기장을 발생시킨다는 점은 동일하다.

다만, 외부에서 공급하던 전류가 차단되면 축전기는 축적했던 전하를 잃는 반면 플로팅게이트는

여전히 전하를 저장하고 있다는 차이가 있다.

이러한 특성때문에 전원을 공급하지 않았을시 DRAM은 데이터를 잃는 휘발성 메모리,

NAND는 데이터를 저장하는 비휘발성 메모리로 구분된다.

그림. DRAM의 구조 그림. NAND의 구조

11) Probe Test

그림. Probe Test

전공정의 과정을 통해 웨이퍼 위에 회로가 완성되면, 구현된 회로들을 Test 하는 과정을 거친다.

불량인 회로들은 2차적인 작업을 통해 바로잡거나 제거한다.

Probe Test가 제대로 이루이지 않으면 필요없는 회로들까지 패키지 과정을 거치게 되므로,

공정의 효율화를 위해 반드시 필요한 과정이다.

Probe Test는 통상적으로 5가지의 과정을 거친다. 1) EPM Test는 회로의 전기적 특성을 검사한다.

다이(Die)가 설계한 것과 같이 정상적인 작동을 보여주는지를 테스트 하는 과정이다.

검사 내용은 반도체의 목적에 따라 달라지지만, 대체로 130여개의 항목을 테스트 한다.

2) 스트레스 테스트는 웨이퍼의 회로가 특정 상황을 견디는지 판별하는 Test를 진행한다.

전자제품에 실장되는 반도체는 일정 이상의 전압과 온도를 견뎌야 한다.

전기적 스트레스는 4.5V~5.5V의 전압을 이용하고, 온도 스트레스 테스트는 100~125도의

환경 내에서 수행한다.

3) 앞선 2개의 테스트를 거친뒤 문제없는 다이를 통과시키거나,

불량한 다이의 수정 여부를 결정한다.

다이 하나에 불량 셀이 소수일 경우, 해당 셀들만 스페어 셀로 교체하여 수정이 가능하다.

4) 수리가 가능하다고 판단되는 Die는 레이저를 이용해 수정된다.

5) 수정된 다이에 대해 위의 테스트 과정을 다시 진행한다.

모든 과정을 통과한 다이 만이 다음 과정인 패키징 공정을 진행할 수 있다.

12) Grinding / Wafer Saw

그림. Grinding / Wafer Saw

Probe Test를 마친 반도체 칩은 전자제품에 실장이 가능하도록 패키징 되는 과정을 거친다.

패키징은 전자제품과 전기적 신호를 연결하며 반도체 칩을 외부로부터 보호한다.

웨이퍼를 패키징 하기 위해, 웨이퍼의 두께를 줄이는 작업이 Grinding 공정이다.

Wafer 연마용 다이아몬드 휠로 회로가 없는 웨이퍼의 뒷면을 연마하여 패키지의

사이즈에 맞게 Grinding 한다.

Grinding 작업을 마친 Wafer 는 개별 칩으로 분리하는 과정을 거친다.

Wafer 절단용 다이아몬드 블레이드를 사용하며,

고속 회전에 의해 웨이퍼를 개별 칩으로 분리한다.

그림. Back Grind 그림. Wafer Saw

13) Die Attach / Wire Bonding

그림. Die Attach / Wire Bonding

Probe Test에서 양품으로 판단된 칩은 Wafer 상에서 떼어내 이를 외부화 전기적 연결을 하는

단자인 Substrate 기판에 접착한다.

Lead Frame 위에 칩(Die)를 접착하기 때문에 Die Attach 공정이라 부른다.

접착 후 칩과 Substrate 기판 사이에 전기적 연결을 위해, Gold Wire로 칩과 Substrate를

연결하는 작업이 Wire Bonding 공정이다.

그림. Die Attach 그림. Wire Bond

14) Molding / Marking

그림. Molding / Marking

Substrate와의 전기적 연결이 완료되면, 칩을 보호하기 위한 Molding 공정을 거친다.

Molding 은 습기, 열, 물리적 충격에서 칩을 보호하기 위해 에폭시몰딩컴파운드(EMC)로 칩을

감싸주는 공정이다.

Molding 공정에서는 EMC를 180도에서 녹여준 후, 회로기판상의 반도체 칩에

도포하는 과정을 거친다.

이후 표면에 레이저를 통해 제조사 및 제품번호를 각인하는 Marking 공정을 수행한다.

그림. Molding 그림. Marking

15) Package Test

그림. Package Test

패키징 공정이 완료되면, 이 패키지가 정상적으로 작동하는지 확인하는 패키지 테스트를 거친다.

패키지 형태 제품의 최종 불량유무를 선별하는 검사이다.

완제품 형태를 갖춘 후 검사가 진행되어 Final Test 라고도 불린다.

테스트 장비 안에서 다양한 조건의 전압, 전기신호, 온도 등의 환경을 조성해 제품의 전기적

특성과 동작이 정상적으로 이뤄지는지 검사한다.

패키지 테스트는 주로 Assembly Out, Burn-in, Mornitoring Burn-in, Post Burn,

Final Test 등이 있다.

Assembly Out은 패키지의 종류, 수량, Spec 등을 확인화는 테스트다. 제품의 당초 설계와

목적에 맞추어 정상적으로 생산되었는지 검사한다. Burn-in 테스트는 불량 가능성이 있는

제품을 제거하기 위한 공정이다.

제품에 고전압, 고온, 전기신호등 극한 조건을 가한 후에, 이후에도 제품이 정상적으로

작동하는지 검사한다.

Mornitoring Burn-in 테스트는 극한고전업, 고운등 극한 조건이 가해지는 상태에서 제품이

정상적으로 동작하는지 확인한다.

Burn-in 테스트에 비해 분석 기간을 단축할 수 있는 장점이 있다.

Post Burn Test는 상온 및 저온 공간에서, Final Test는 다시 고온에서 제품 동작의

이상유무를 확인한다.

이러한 테스트를 반복적으로 거친 후에도 문제가 없는 제품만 출하되게 된다.

Burn-in 테스트 과정에선 환경 조건을 조성하는 테스트 장비 외에도, 테스트 과정에서 패키지와

접촉하여 칩의 정상 작동 유무를 테스트 장비에 전달하는 테스트 소켓이 사용된다.

테스트 소켓은 여러 환경에 지속적으로 노출되어 일정 횟수 사용 후 교체해야 하는

소모성 부품이다.

그림. Burn - in 테스트 소켓

16) 패키지의 유형

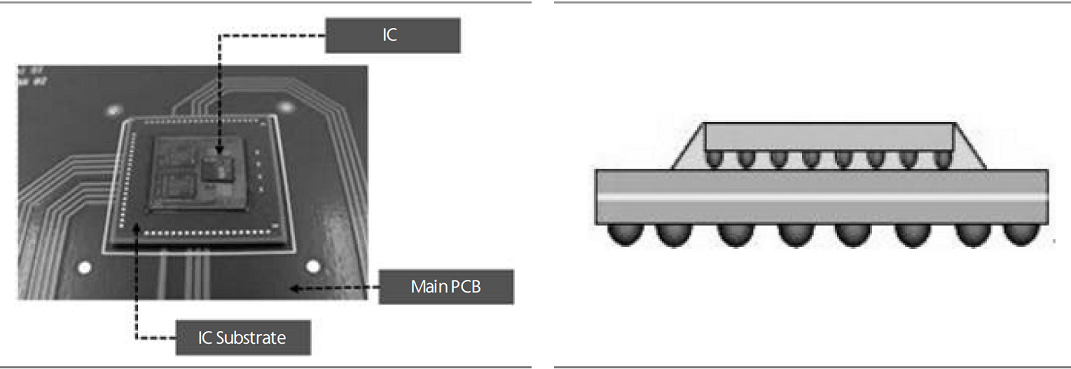

패키지는 칩과 Substrate의 연결 방식, Substrate와 PCB간의 연결방식에 따라 구분된다.

칩과 Substrate의 연결은 Wire Bonding과 Flip Chip Bonding으로 구분된다.

Wire Bonding은 금 와이어를 통해 칩과 Substrate를 연결하는 전통적인 방법이다.

Flip Chip Bonding은 칩의 상단에 Bumb를, Substrate 상단에 Pad를 형성하여 열압착등의

방법을 통해 접속시킨다.

구조상 칩이 뒤집힌 상태로 Substrate와 접속되어 Flip Chip 이라는 용어를 사용한다.

와이어 방식 대비 전기적 특성이 향상되나, 부착과정에서 칩이 손상될 우려가 있다.

그림. Wire Bonding 그림. Flip Chip Bonding

Substrate와 PCB의 결합방식은 주로 BGA(Ball Grid Array),PGA(Pin Grid Array),

LGA(Land Grid Array) 방식 사용한다.

BGA 방식은 솔더볼을 이용해 메인 PCB와 접속하는 방식이다.

칩을 보호하는 패키징 소재 에 따라 PBGA(Plastic), CBGA(Ceramic), TBGA(Tape) 으로 분류된다.

한번 실장을 하면 탈 부탁이 불가능한 방식이다.

PGA 방식은 Substrate에 Pin을 만들어 메인 PCB 상의 소켓을 통해 접속하는 방식이다.

데스크탑 메인보드의 CPU와 같이 탈부착이 필요한 부품에 주로 사용된다.

PGA 방식은 Pin 의 간격이 최소 1.27mm로 제한되어, Substrate의 크기가 칩에 비에 크다는

단점이 있다.

LGA 방식은 Substrate에 Land(패드), 메인 PCB에 탄성을 가진 핀 소켓을 탑재하는 방식 이다.

PGA 방식대비 Substrate 제조원가 감소, 패키지 크기가 감소한다.

그림. PCB에 실장된 IC Substrate 그림. BGA – Ball Grid Array

그림. PGA – Pin Grid Array 그림. LGA – Land Grid Array

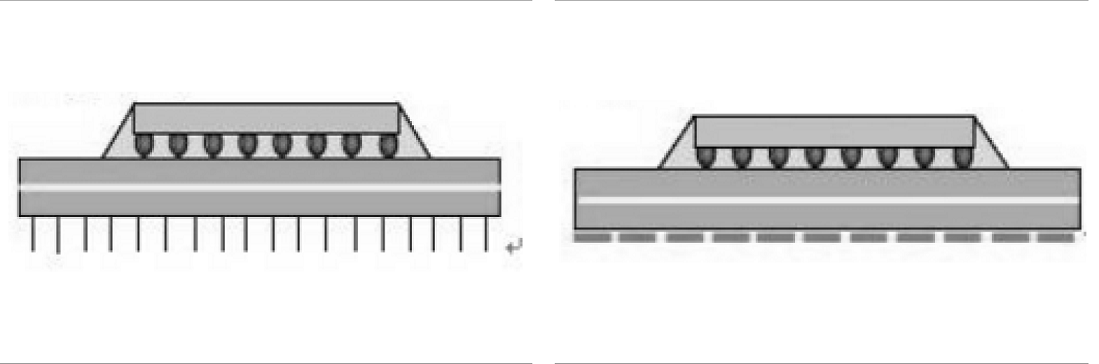

패키징 방식중CSP(Chip Scale Package)는 찹과 크기가 같거나 약간 큰(1.2배 이내)

IC Substrate를 사용하는 방식이다.

경박단소화가 필요한 스마트폰류의 전자기기에 주로 사용되며, 두께, 크기, 입출력수, 층수가

적다는 점 외에는 PBGA 방식과 동일하다.

사용 용도에 따라 MCP(Multi Chip Package), SiP(System in Package), BOC(Board On Chip)

등으로 분류된다.

MCP(Multi Chip Package)는 여러개의 칩을 수직으로 쌓아서 만든 IC Substrate 이다.

실장면적 및 제조비용이 감소한다. 수평뿐만 아니라 개별적으로 작동하는 다양한 칩을 하나로

패키징한 방식이 SiP(System in Package)이며, 칩의 동작 특성이 향상하는 효과가 있다.

BOC(Board On Chip)는 DRAM에서 이용되는 패키징 방식이다. DRAM의 경우 입출력 부분이

일반적인 반도체와 달리 칩 중앙에 배열된다. 따라서, 기존의 리드 프레임에 칩을 부착하는

방식은 고속의 메모리에 적합하지 않다.

BOC는 칩을 몸체 가운데의 빈 공간을 통해 와이어 본딩을 통해 연결한다.

그림. MCP – Multi Chip Package 그림. BOC – Board On Chip

1대에 1500억, 이 장비를 확보해야 반도체 패권 - 조선일보 - 2020.12.30 news.v.daum.net/v/20201230163052747

'IT 인터넷 이야기' 카테고리의 다른 글

| Apple Moonshot, 애플 글래스 (Forbes) (0) | 2020.06.09 |

|---|---|

| 배터리 구조 이해하기 (0) | 2020.06.01 |

| 전고체 배터리는 무엇이고 , 언제 될까 (0) | 2020.05.30 |

| 스마트폰 전망 (0) | 2018.02.11 |

| MS 기술 그루 키프만 "스마트폰 시대 끝났다" (0) | 2017.05.10 |